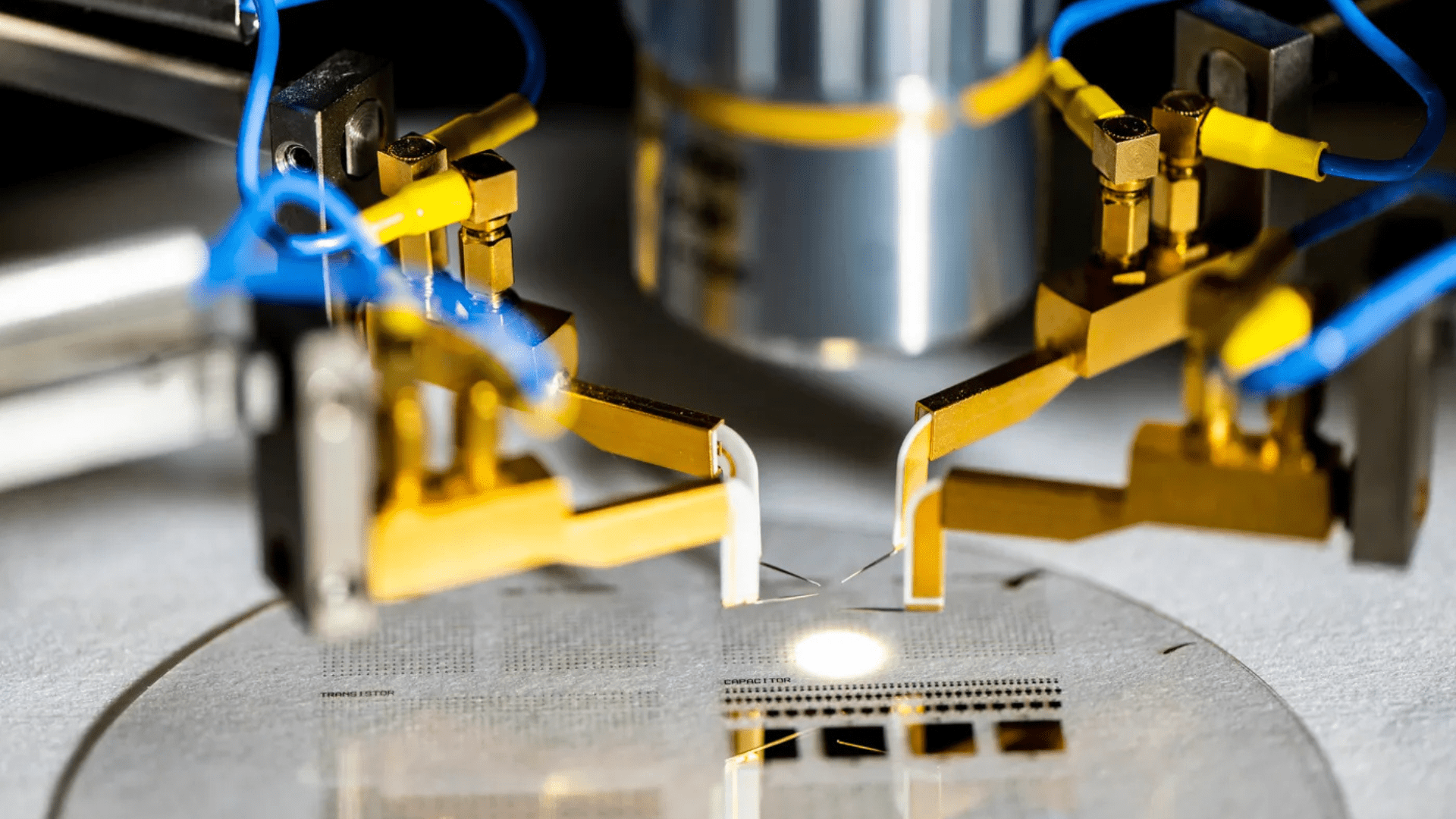

A professor at Northeastern University in Boston, Massachusetts, is on the brink of slashing the cost of producing chips with a revolutionary new nanomanufacturing process.

Professor Ahmed A. Busnaina patented a new nanomanufacturing process and printer that can manufacture advanced technology and chips more efficiently and at a fraction of the conventional cost. Additionally, it’s capable of making them on a nanoscale.

Chips at a Fraction of the Cost

“I thought that there must be an easier way to do this, there must be a cheaper way to do this,” said Busnaina, the William Lincoln Smith professor and professor at Northeastern University. “We started, basically, with very simple physical chemistry with a very simple approach.”

Current microelectronics manufacturing methods are expensive, slow, and require many resources. Busnaina explains that the conventional method of microelectronics fabrication deposits multiple layers of thin film, each representing one part of the circuit, which eventually builds up to create a microprocessor or a memory chip. He said that for each material used, there is a different process. In addition, there are many excess deposits, and the process “etches away” the excess.

In short, the professor says a major drawback of this method is its cost. According to Northeastern University, facilities to fabricate the advanced technology and chips cost about $20 to $40 billion just to build and another $1 billion to operate annually.

Because of the cost, the number of companies capable of building the chips went from 29 in the early 2000s to five in 2018. Busnaina explains that this translates into a six-month to a year timeline just to make a chip and a similar timeline if it needs to be revised.

Bottoms-Up Process

Busnaina believed that needed to change. His answer was to develop a “bottoms-up” nanomanufacturing process for silicon microprocessors or memory chips. According to the professor, it lowers the manufacturing cost to 1% of the conventional method. Instead of chipping away at excess deposits, it builds up. Kind of like sculpting something, he says.

“We don’t remove anything,” he continued. “We only deposit the material we need at the location we need it.”

He says the materials can be deposited faster using very small particles, which enables one to create very small objects in a fraction of the time. “We showed that we can do structures down to 25 nanometers in one minute, for example, over a large area,” Busnaina said. “So it’s high throughput, very low cost.”